How exclusive works. Basic logic elements

The operation excluding or (unequivocally, addition of two) is denoted by the symbol and differs from logical or only at \u003d 1 and b \u003d 1.

Thus, the unequalness of the two statements X1 and X2 call such a statement y, which is truly then and only when one of these statements are truly true, and the other is false.

The definition of this operation can be recorded in the form of a truth table (Table 6):

Table 6 - Tatac of the truth of the operation "excluding or"

As can be seen from Table 6, the logic of the element corresponds to its name.

This is the same element "or" with one small difference. If the value at both inputs is equal to a logical unit, then at the output of the element "excluding or", unlike the element "or", not a unit, and zero.

The operation "excluding or" actually compares the coincidence of two binary discharge.

Each logical bunch is considered as an operation on logical statements and has its name and designation (Table 7).

Table 7 - Basic Logic Operations

|

Designation operations |

Reading |

Name of operation |

Alternative notation |

|

Denial (inversion) |

Damn from above |

||

|

Conjunction (logical multiplication) | |||

|

Dysjunction (logical addition) | |||

|

If ... |

Amplication |

|

|

|

Then and only then |

Equivalence | ||

|

Or either |

Excluding or (addition by module 2) |

|

The procedure for performing logical operations in complex logical terms

The system of logical operations of inversion, conjunction, disjunction allows us to build an arbitrarily complex logical expression.

When calculating the value of the logical expression, a certain procedure for performing logical operations is adopted.

1. Inversion.

2. Conjunction.

3. Dysuunction.

4. implication.

5. Equivalence.

To change the specified procedure for performing operations, brackets are used.

Logic expressions and truth tables

Logic expressions

Each composite statement can be expressed in the formula (logical expression), which includes logical variables denoting statements and signs of logical operations denoting logical functions.

To write a composite statement in the form of a logical expression in the formal language (the language of the Logic algebra) in a composite statement, it is necessary to allocate simple statements and logical connections between them.

We write in the form of a logical expression composite statement "(2 · 2 \u003d 5 or 2 ∙ 2 \u003d 4) and (2 ∙ 2 ≠ 5 or 2 ∙ 2 ≠four)".

Let's analyze the composite statement. It contains two simple statements:

A \u003d "2 2 \u003d 5" -den (0),

B \u003d "2 2 \u003d 4" - internal (1).

Then the composite statement can be written in the following form:

«( BUT orIN) and (ā orIN)».

Now it is necessary to record a statement in the form of a logical expression, taking into account the sequence of logical operations. When performing logical operations, the following procedure for their execution is defined:

inversion, conjunction, disjunction.

To change the specified order, brackets can be used:

F. = (A.v.IN) & (Ā v.IN).

The truth or the falsity of composite statements can be determined purely formally, guided by the laws of algebra of statements, not referring to the semantic content of statements.

We substitute the value of logical variables in the logical expression and, using the truth tables of basic logic operations, we obtain the value of the logical function:

F. \u003d (A V c) & ( Ā V c) \u003d (0 V 1) & (1 V 0) \u003d 1 ° C 1 \u003d 1.

Tatasets of truth

Tables in which logical operations reflect the results of computing complex statements with different values \u200b\u200bof the initial simple statements are called truth tables.

Simple statements are denoted by variables (for example, a and b).

When constructing truth tables, it is advisable to be guided by a certain sequence of actions:

it is necessary to determine the number of rows in the truth table. It is equal to the number of possible combinations of values \u200b\u200bof logical variables included in a logical expression. If the number of logical variables is equal p, then:

number of rows \u003d 2 n. .

In our case, the logical function

has 2 variables and, therefore, the number of rows in the truth table should be 4;

it is necessary to determine the number of columns in the truth table, which is equal to the number of logical variables plus the number of logical operations.

In our case, the number of variables is two: A and B, and the number of logical operations is five (Table 8), that is, the number of columns of the truth table is equal to seven;

it is necessary to build a truth table with the specified number of rows and columns, designate columns and add possible sets of initial logical variables to the table;

you must fill in the truth table by columns by performing basic logic operations in the required sequence and in accordance with their truth tables.

Now we can determine the value of a logical function for any set of values \u200b\u200bof logical variables.

Table 8 - Total Tank of Logic Function

In practice, two-level elements "excluding or are most often used. In fig. 1 shows the conditional graphic designation of the element without inversion and its status table. By simple, the essence of this element is reduced to the following, the output signal appears only when the logical levels at the inputs are not the same.

Scheme of the selection of the front and cutting of the pulse

In this scheme, the three elements "excluding or" are used to delay pulses. DD1.4 - summing. The output pulses have stable fronts and sections. The duration of each output pulse is equal to the tripled time delay delay of each of the three elements. The time interval between the front of the output pulses is equal to the duration of the input pulse. Also, this device doubles the frequency of the input signal.

There is another interesting property "excluding or". If one of the inputs are permanent "0", the signal at the element output will repeat the input signal, and if the permanent "0" change to the permanent "1", the output signal will already be inversion inversion.

Sometimes there is a need to obtain an element "excluding or" from individual standard logical elements. An example is the "excluding or" 2-or-no. Figure 3 shows the "excluding or" scheme in four states. Here are all possible logical levels on each of the logically used elements 2-not.

Such elements are included in the scheme. In this scheme, the element "excluding or" is made on four elements of 2-or-non-nominated K561L7 chip.

Discrete Signal Shaper Signal

The diagram of the former is shown in Figure 4. Here, the logical element "excluding or" is also implemented on four elements 2-or-not.

At the inputs 1 and 2 of the formator, the pulses of the rectangular shape fall (see graphics 1 and 2), which differ in the following frequency. The node on the logical elements of DD1.1-DDI.4 variables these signals. The output pulse signal (graph 3) from the DD1.4 element is fed to an integrating circuit R3, C1, converting it into a triangular signal (graph 4) with a frequency equal to the difference in the frequencies of input signals, and the DA1 is converting the received signal to the meander (see. Schedule 5). The R1 resistor regulate the duration of the positive and negative half-hole output signal. Very interesting scheme. Radio constructor, there is something to think about. For example, the signal shown in the third graph is the Sinusoid PWM signal.

Of course, the range of use of elements "excluding or" is much wider. I brought here in my opinion more interesting for radio amateurs.

| Login 1. | Login 2. | Output |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Fig. 4.1.

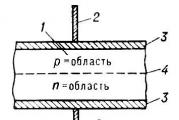

Under the function, excluding or refers to the following: The unit at the output appears when only one input is present. If the units on the inputs are two or more, or if at all the inputs of zero, then the output will be zero. Tank truth The two-time element is excluding or given in Table. 4.1. Designations adopted in domestic and foreign circuits are shown in Fig. 4.1. The inscription on the domestic designation of the element is excluding or "\u003d 1" just indicates that the situation is distinguished when one and only one unit is on the inputs.

Elements excluding or in standard series a bit. The domestic series offer LP5 chips (four two-axis elements with 2C output), LL3 and LP12, differ from LP5 OK output. Too specific function is implemented by these elements.

From the point of view of mathematics, the element excluding or performs the operation of the so-called summation of module 2. Therefore, these elements are also called the adders in the module two. As already noted in the previous lecture, the summation of module 2 is a plus sign enclosed in a circle.

The main use of elements excluding or, directly the following tatasets of truthIt consists in comparing two input signals. In the case when two units or two zero come to the inputs (signals coincide), zero is formed at the output (see Table 4.1). Usually, with this application, a permanent level is supplied to one element input, with which the time-changing signal comes to another input. But significantly more often for comparison of signals and codes apply special chips comparators Codovwhich will be discussed in the next lecture.

As an adder module 2, the element is excluding or used in parallel and consecutive divisors for module 2, which serve to calculate cyclic checks. But these schemes will be discussed in detail in lectures 14.15.

Important use of elements excluding or is a managed inverter (Fig. 4.2). In this case, one of the element inputs is used as a manager, and an information signal comes to another element. If the unit is input, then the input signal is inverted if zero is not inverted. Most often control signal Set by a constant level by defining the mode of the element, and the information signal is pulsed. That is, an element excluding or can change the polarity of the input signal or front, and may not be changed depending on control signal.

Fig. 4.2.

In the case when there are two signals of the same polarity (positive or negative), and at the same time their simultaneous arrival is excluded, the element is excluding or can be used to mix these signals (Fig. 4.3). With any polarity of the input signals, the output signals of the element will be positive. With positive input signals, the element excluding or will operate as an element 2, and with negative it will replace the element 2I - not. Such replacements may be useful in cases where some elements excluding or are left in the diagram. True, it should be borne in mind that distribution delay The signal in the element is excluding or usually somewhat larger (about 1.5 times) than the delay in the simplest elements and, and non, or, or non.

Absolutely all digital chips consist of the same logical elements - "bricks" of any digital node. Here we will talk about them now.

Logical element - This is a scheme that has several inputs and one output. Each state of signals on the inputs corresponds to a specific output signal.

So what elements come?

Element "And" (and)

Otherwise, it is called "conjunct".

In order to understand how it works, you need to draw a table in which the output states will be listed at any combination of input signals. Such a table is called " tank truth" Total Tables are widely used in digital technology to describe the operation of logic schemes.

This is what the element "and" and its truth table looks like:

Because you have to communicate with both Russian and bourgeois tech. Documentation, I will lead conditional graphics symbols (HBO) of elements and on our and on not our standards.

We look at the truth table, and clarify the principle in the brain. It is not difficult to understand it: the unit at the output of the element "and" occurs only when the units are filed on both inputs. This explains the name of the element: units must be on one, and on another entrance.

If you see a bit differently, you can say so: at the output of the element "and" will be zero in the event that at least one of its inputs is served. Remember. Go ahead.

Element "or" (OR)

Otherwise, his name is "disjunctor".

We admire:

Again, the name speaks for itself.

At the output, a unit occurs when one or another or on both immediately the input is filed. This element can also be called the "and" element for negative logic: zero on its output is only if the zeros are applied to one and on the second input.

Element "Not" (not)

More often, it is called "inverter".

Need something to talk about his work?

Element "and not" (Nand)

The element and is not working in the same way as "and", only the output signal is completely opposite. Where the element "and" at the output should be "0", the element "and not" is a unit. And vice versa. E E is easy to understand the equivalent diagram of the element:

Element "Or-Not" (NOR)

The same story is an element "or" with an inverter at the exit.

The next comrade is arranged a few cunning:

Element "excluding or" (XOR)

He is like this:

The operation he performs is often called "adding modulo 2". In fact, digital adders are built on these elements.

We look at the truth table. When at the output of the unit? That's right: when different signals are inputs. On one - 1, on the other - 0. This is such a cunning.

The equivalent scheme is approximately as follows:

It is not necessary to memorize it.

Actually, this is the main logical elements. They are based on absolutely any digital chips. Even your favorite pentium 4.

Well, finally, there are several microcircuits inside which digital elements are contained. About the conclusions of the elements indicate the numbers of the corresponding feet of the chip. All microcircuits listed here have 14 legs. Power is supplied on legs 7 (-) and 14 (+). Power supply - see the table in the previous paragraph.

Often, in order to demonstrate the limited capabilities of single-layer perceptrons when solving problems, it is resorted to the consideration of the so-called problem. Xor - exclusive or.

The essence of the task is to be as follows. The logical function XOR is excluding or. This function is from two arguments, each of which can be zero or unit. It takes a value when one of the arguments is equal to one, but not both, otherwise. The problem can be illustrated using a single-layer single-stage system with two inputs shown in the figure below.

Denote one input through, and the other through, then all their possible combinations will consist of four points on the plane. The table below shows the required link between the inputs and the output, where the input combinations that should give zero output are labeled and, a single output - and.

| Points | Value | Value | Required output |

| 0 | 0 | 0 | |

| 1 | 0 | 1 | |

| 0 | 1 | 1 | |

| 1 | 1 | 0 |

One neuron with two inputs can form a decisive surface in the form of an arbitrary straight line. In order for the network to implement the XOR function, the specified table above, you need to position the direct so that the points be on one side of the straight, and the point is on the other. Having tried to draw such a straight line in the figure below, we make sure it is impossible. This means that whatever values \u200b\u200bare attributed to the scales and threshold, a single-layer neural network is unable to reproduce the ratio between the input and output required to represent the XOR function.

However, the XOR function is easily formed by a two-layer network, and in many ways. Consider one of these ways. We upgrade the network in the figure, adding another hidden layer of neurons:

Note that this network is given as it is, i.e. We can assume that it is already trained. The numbers above the arrows show the values \u200b\u200bof synaptic scales. As an activation function, we will apply the function of a single jump with a threshold having the following chart:

Then the result of the operation of such a neural network can be represented as the following table:

| Points | Value | Value | Required output | |||

| 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 |

Each of the two neurons of the first layer forms a decisive surface in the form of an arbitrary straight line (divides the plane into two half-planes), and the neuron of the output layer combines these two solutions, forming a decisive surface in the form of a strip formed by parallel straight neurons of the first layer:

The neural network used in this article to solve the XOR task is primitive and does not use all the capabilities of multi-layer networks. It is obvious that multilayer neural networks have a greater representing capacity than single-layer, only in the case of the presence of nonlinearity. And in this network, a threshold linear activation function is applied. Such a network cannot be trained, for example, by applying an error inversely distribution algorithm.