Как работает исключающее. Базовые логические элементы

Операция исключающее ИЛИ (неравнозначность, сложение по модулю два) обозначается символом и отличается от логического ИЛИ только приA=1 и B=1.

Таким образом, неравнозначность двух высказываний Х1 и Х2 называют такое высказывание Y, которое истинно тогда и только тогда, когда одно из этих высказываний истинно, а другое ложно.

Определение данной операции может быть записано в виде таблицы истинности (таблица 6):

Таблица 6 – Таблица истинности операции «ИСКЛЮЧАЮЩЕЕ ИЛИ»

Как видно из таблицы 6, логика работы элемента соответствует его названию.

Это тот же элемент «ИЛИ» с одним небольшим отличием. Если значение на обоих входах равно логической единице, то на выходе элемента «ИСКЛЮЧАЮЩЕЕ ИЛИ», в отличие от элемента «ИЛИ», не единица, а ноль.

Операция «ИСКЛЮЧАЮЩЕЕ ИЛИ» фактически сравнивает на совпадение два двоичных разряда.

Каждая логическая связка рассматривается как операция над логическими высказываниями и имеет своё название и обозначение (таблица 7).

Таблица 7 – Основные логические операции

|

Обозначение операции |

Читается |

Название операции |

Альтернативные обозначения |

|

Отрицание (инверсия) |

Черта сверху |

||

|

Конъюнкция (логическое умножение) | |||

|

Дизъюнкция (логическое сложение) | |||

|

Если … то |

Импликация |

|

|

|

Тогда и только тогда |

Эквиваленция | ||

|

Либо … либо |

ИСКЛЮЧАЮЩЕЕ ИЛИ (сложение по модулю 2) |

|

Порядок выполнения логических операций в сложном логическом выражении

Система логических операций инверсии, конъюнкции, дизъюнкции позволяет построить сколь угодно сложное логическое выражение.

При вычислении значения логического выражения принят определённый порядок выполнения логических операций.

1. Инверсия.

2. Конъюнкция.

3. Дизъюнкция.

4. Импликация.

5. Эквивалентность.

Для изменения указанного порядка выполнения операций используются скобки.

Логические выражения и таблицы истинности

Логические выражения

Каждое составное высказывание можно выразить в виде формулы (логического выражения), в которую входят логические переменные, обозначающие высказывания, и знаки логических операций, обозначающие логические функции.

Для записи составного высказывания в виде логического выражения на формальном языке (языке алгебры логики) в составном высказывании нужно выделить простые высказывания и логические связи между ними.

Запишем в форме логического выражения составное высказывание «(2·2=5 или 2∙2=4) и (2∙2≠5 или 2∙2 ≠4)».

Проанализируем составное высказывание. Оно содержит два простых высказывания:

А = «2 2=5»-ложно (0),

В = «2 2=4»-истинно (1).

Тогда составное высказывание можно записать в следующей форме:

«(А или В ) и (Ā или В )».

Теперь необходимо записать высказывание в форме логического выражения с учётом последовательности выполнения логических операций. При выполнении логических операций определён следующий порядок их выполнения:

инверсия, конъюнкция, дизъюнкция.

Для изменения указанного порядка могут использоваться скобки:

F = (A v В ) & (Ā v В ).

Истинность или ложность составных высказываний можно определять чисто формально, руководствуясь законами алгебры высказываний, не обращаясь к смысловому содержанию высказываний.

Подставим в логическое выражение значения логических переменных и, используя таблицы истинности базовых логических операций, получим значение логической функции:

F = (A v В) & (Ā v В) = (0 v 1) & (1 v 0) = 1 & 1 = 1.

Таблицы истинности

Таблицы, в которых логические операции отражают результаты вычислений сложных высказываний при различных значениях исходных простых высказываний, называются таблицами истинности.

Простые высказывания обозначаются переменными (например, A и B).

При построении таблиц истинности целесообразно руководствоваться определённой последовательностью действий:

необходимо определить количество строк в таблице истинности. Оно равно количеству возможных комбинаций значений логических переменных, входящих в логическое выражение. Если количество логических переменных равно п, то:

количество строк = 2 n .

В

нашем случае логическая функция

имеет 2 переменные и, следовательно, количество строк в таблице истинности должно быть равно 4;

необходимо определить количество столбцов в таблице истинности, которое равно количеству логических переменных плюс количество логических операций.

В нашем случае количество переменных равно двум: А и В, а количество логических операций - пяти (таблица 8), то есть количество столбцов таблицы истинности равно семи;

необходимо построить таблицу истинности с указанным количеством строк и столбцов, обозначить столбцы и внести в таблицу возможные наборы значений исходных логических переменных;

необходимо заполнить таблицу истинности по столбцам, выполняя базовые логические операции в необходимой последовательности и в соответствии с их таблицами истинности.

Теперь мы можем определить значение логической функции для любого набора значений логических переменных.

Таблица 8 – Таблица истинности логической функции

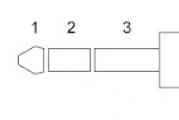

На практике наиболее часто используют двухвходовые элементы «исключающее ИЛИ. На рис. 1 показано условное графическое обозначение элемента без инверсии и его таблица состояний. По простому, суть данного элемента сводится к следующему, сигнал на выходе появляется только в том случае, когда логические уровни на входах не одинаковые.

Схема выделения фронта и среза импульса

В данной схеме три элемента «Исключающий ИЛИ» используются для задержки импульсов. DD1.4 — суммирующий. Выходные импульсы имеют стабильные фронты и срезы. Длительность каждого выходного импульса равна утроенному времени задержки переключения каждого из трех элементов. Временной промежуток между фронтами выходных импульсов равен длительности входного импульса. Так же это устройство удваивает частоту входного сигнала.

Есть еще одно интересное свойство «Исключающее ИЛИ». Если на один из входов подать постоянный «0», то сигнал на выходе элемента будет повторять входной сигнал, а если постоянный «0» поменять на постоянную «1», то выходной сигнал уже будет инверсией входного.

Иногда появляется необходимость получить элемент «исключающее ИЛИ» из отдельных стандартных логических элементов. Примером может служить схема элемента «исключающее ИЛИ» реализованная на четырех элементах 2-И-НЕ. На рисунке 3 показана схема «исключающее ИЛИ» в четырех ее состояниях. Здесь показаны все возможные логические уровни на каждом из используемых логически элементов 2-И-НЕ.

Такие элементы входят в схему . В данной схеме элемент «Исключающий ИЛИ» выполнен на четырех элементах 2-И-НЕ, входящих в один корпус микросхемы К561ЛА7.

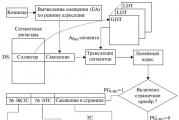

Формирователь дискретного сигнала с разностной частотой

Схема формирователя показана на рисунке 4. Здесь логический элемент «исключающее ИЛИ» также реализован на четырех элементах 2-И-НЕ.

На входы 1 и 2 формирователя падают импульсы прямоугольной формы (см. графики 1 и 2), которые различаются частотой следования. Узел на логических элементах DD1.1-DDI.4 перемножает эти сигналы. Выходной импульсный сигнал (график 3) с элемента DD1.4 подается на интегрирующую цепь R3, С1, преобразующую его в сигнал треугольной формы (график 4) с частотой, равной разности частот входных сигналов, а ОУ DA1 преобразует полученный сигнал в меандр (см. график 5). Резистором R1 регулируют длительность положительной и отрицательной полуволн выходного сигнала. Очень интересная схема. Радиоконструктору, есть над чем подумать. Например, сигнал, показанный на третьем графике, является сигналом ШИМ синусоиды.

Конечно диапазон использования элементов «исключающее ИЛИ» намного шире. Я привел здесь на мой взгляд более интересные для радиолюбителей.

| Вход 1 | Вход 2 | Выход |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Рис.

4.1.

Под функцией Исключающее ИЛИ понимается следующее: единица на выходе появляется тогда, когда только на одном входе присутствует единица . Если единиц на входах две или больше, или если на всех входах нули, то на выходе будет нуль. Таблица истинности двухвходового элемента Исключающее ИЛИ приведена в табл. 4.1. Обозначения, принятые в отечественных и зарубежных схемах, показаны на рис. 4.1. Надпись на отечественном обозначении элемента Исключающее ИЛИ "=1" как раз и обозначает, что выделяется ситуация, когда на входах одна и только одна единица .

Элементов Исключающее ИЛИ в стандартных сериях немного. Отечественные серии предлагают микросхемы ЛП5 (четыре двухвходовых элемента с выходом 2С), ЛЛ3 и ЛП12, отличающиеся от ЛП5 выходом ОК. Слишком уж специфическая функция реализуется этими элементами.

С точки зрения математики, элемент Исключающее ИЛИ выполняет операцию так называемого суммирования по модулю 2. Поэтому эти элементы также называются сумматорами по модулю два. Как уже отмечалось в предыдущей лекции, обозначается суммирование по модулю 2 знаком плюса, заключенного в кружок.

Основное применение элементов Исключающее ИЛИ, прямо следующее из таблицы истинности , состоит в сравнении двух входных сигналов. В случае, когда на входы приходят две единицы или два нуля (сигналы совпадают), на выходе формируется нуль (см. табл. 4.1) . Обычно при таком применении на один вход элемента подается постоянный уровень, с которым сравнивается изменяющийся во времени сигнал, приходящий на другой вход. Но значительно чаще для сравнения сигналов и кодов применяются специальные микросхемы компараторов кодов , которые будут рассмотрены в следующей лекции.

В качестве сумматора по модулю 2 элемент Исключающее ИЛИ используется также в параллельных и последовательных делителях по модулю 2, служащих для вычисления циклических контрольных сумм. Но подробно эти схемы будут рассмотрены в лекциях 14,15.

Важное применение элементов Исключающее ИЛИ - это управляемый инвертор (рис. 4.2) . В этом случае один из входов элемента используется в качестве управляющего, а на другой вход элемента поступает информационный сигнал. Если на управляющем входе единица , то входной сигнал инвертируется, если же нуль - не инвертируется. Чаще всего управляющий сигнал задается постоянным уровнем, определяя режим работы элемента, а информационный сигнал является импульсным. То есть элемент Исключающее ИЛИ может изменять полярность входного сигнала или фронта, а может и не изменять в зависимости от управляющего сигнала .

Рис. 4.2.

В случае, когда имеется два сигнала одинаковой полярности (положительные или отрицательные), и при этом их одновременный приход исключается, элемент Исключающее ИЛИ может быть использован для смешивания этих сигналов (рис. 4.3) . При любой полярности входных сигналов выходные сигналы элемента будут положительными. При положительных входных сигналах элемент Исключающее ИЛИ будет работать как элемент 2ИЛИ, а при отрицательных он будет заменять элемент 2И-НЕ. Такие замены могут быть полезны в тех случаях, когда в схеме остаются неиспользованными некоторые элементы Исключающее ИЛИ. Правда, при этом надо учитывать, что задержка распространения сигнала в элементе Исключающее ИЛИ обычно несколько больше (примерно в 1,5 раза), чем задержка в простейших элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ.

Абсолютно все цифровые микросхемы состоят из одних и тех же логических элементов – «кирпичиков» любого цифрового узла. Вот о них мы и поговорим сейчас.

Логический элемент – это такая схемка, у которой несколько входов и один выход. Каждому состоянию сигналов на входах, соответствует определенный сигнал на выходе.

Итак, какие бывают элементы?

Элемент «И» (AND)

Иначе его называют «конъюнктор».

Для того, чтобы понять как он работает, нужно нарисовать таблицу, в которой будут перечислены состояния на выходе при любой комбинации входных сигналов. Такая таблица называется «таблица истинности ». Таблицы истинности широко применяются в цифровой технике для описания работы логических схем.

Вот так выглядит элемент «И» и его таблица истинности:

Поскольку вам придется общаться как с русской, так и с буржуйской тех. документацией, я буду приводить условные графические обозначения (УГО) элементов и по нашим и по не нашим стандартам.

Смотрим таблицу истинности, и проясняем в мозгу принцип. Понять его не сложно: единица на выходе элемента «И» возникает только тогда, когда на оба входа поданы единицы. Это объясняет название элемента: единицы должны быть И на одном, И на другом входе.

Если посмотреть чуток иначе, то можно сказать так: на выходе элемента «И» будет ноль в том случае, если хотя бы на один из его входов подан ноль. Запоминаем. Идем дальше.

Элемент «ИЛИ» (OR)

По другому, его зовут «дизъюнктор».

Любуемся:

Опять же, название говорит само за себя.

На выходе возникает единица, когда на один ИЛИ на другой ИЛИ на оба сразу входа подана единица. Этот элемент можно назвать также элементом «И» для негативной логики: ноль на его выходе бывает только в том случае, если и на один и на второй вход поданы нули.

Элемент «НЕ» (NOT)

Чаще, его называют «инвертор».

Надо чего-нибудь говорить по поводу его работы?

Элемент «И-НЕ» (NAND)

Элемент И-НЕ работает точно так же как «И», только выходной сигнал полностью противоположен. Там где у элемента «И» на выходе должен быть «0», у элемента «И-НЕ» - единица. И наоборот. Э то легко понять по эквивалентной схеме элемента:

Элемент «ИЛИ-НЕ» (NOR)

Та же история – элемент «ИЛИ» с инвертором на выходе.

Следующий товарищ устроен несколько хитрее:

Элемент «Исключающее ИЛИ» (XOR)

Он вот такой:

Операция, которую он выполняет, часто называют «сложение по модулю 2». На самом деле, на этих элементах строятся цифровые сумматоры.

Смотрим таблицу истинности. Когда на выходе единицы? Правильно: когда на входах разные сигналы. На одном – 1, на другом – 0. Вот такой он хитрый.

Эквивалентная схема примерно такая:

Ее запоминать не обязательно.

Собственно, это и есть основные логические элементы. На их основе строятся абсолютно любые цифровые микросхемы. Даже ваш любимый Пентиум 4.

Ну и напоследок – несколько микросхем, внутри которых содержатся цифровые элементы. Около выводов элементов обозначены номера соответствующих ног микросхемы. Все микросхемы, перечисленные здесь, имеют 14 ног. Питание подается на ножки 7 (-) и 14 (+). Напряжение питания – смотри в таблице в предыдущем параграфе.

Часто, для того чтобы продемонстрировать ограниченные возможности однослойных персептронов при решении задач прибегают к рассмотрению так называемой проблемы XOR – исключающего ИЛИ .

Суть задачи заключаются в следующем. Дана логическая функция XOR – исключающее ИЛИ. Это функция от двух аргументов, каждый из которых может быть нулем или единицей. Она принимает значение , когда один из аргументов равен единице, но не оба, иначе . Проблему можно проиллюстрировать с помощью однослойной однонейронной системы с двумя входами, показанной на рисунке ниже.

Обозначим один вход через , а другой через , тогда все их возможные комбинации будут состоять из четырех точек на плоскости. Таблица ниже показывает требуемую связь между входами и выходом, где входные комбинации, которые должны давать нулевой выход, помечены и , единичный выход – и .

| Точки | Значение | Значение | Требуемый выход |

| 0 | 0 | 0 | |

| 1 | 0 | 1 | |

| 0 | 1 | 1 | |

| 1 | 1 | 0 |

Один нейрон с двумя входами может сформировать решающую поверхность в виде произвольной прямой. Для того, чтобы сеть реализовала функцию XOR, заданную таблицей выше, нужно расположить прямую так, чтобы точки были с одной стороны прямой, а точки – с другой. Попытавшись нарисовать такую прямую на рисунке ниже, убеждаемся, что это невозможно. Это означает, что какие бы значения ни приписывались весам и порогу, однослойная нейронная сеть неспособна воспроизвести соотношение между входом и выходом, требуемое для представления функции XOR.

Однако функция XOR легко формируется уже двухслойной сетью, причем многими способами. Рассмотрим один из таких способов. Модернизуем сеть на рисунке, добавив еще один скрытый слой нейронов:

Отметим, что данная сеть дана как есть, т.е. можно считать, что она уже обучена. Цифры над стрелками показывают значения синаптических весов. В качестве функции активации применим функцию единичного скачка с порогом , имеющую следующий график:

Тогда результат работы такой нейронной сети можно представить в виде следующей таблицы:

| Точки | Значение | Значение | Требуемый выход | |||

| 0 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | 0 | 0 |

Каждый из двух нейрон первого слоя формирует решающую поверхность в виде произвольной прямой (делит плоскость на две полуплоскости), а нейрон выходного слоя объединяет эти два решения, образуя решающую поверхность в виде полосы, образованной параллельными прямыми нейронов первого слоя:

Нейронная сеть, используемая в этой статье для решения задачи XOR, примитивна и не использует всех возможностей многослойных сетей. Очевидно, что многослойные нейронные сети обладают большей представляющей мощностью, чем однослойные, только в случае присутствия нелинейности. А в данной сети применена пороговая линейная функция активации. Такую сеть нельзя будет обучить, например, применив алгоритм обратного распространения ошибки.